VGA�$B%b%8%e!<%k$N%7%_%e%l!<%7%g%sJ}K!�(B

VGA�$B%b%8%e!<%k$K$D$$$F$O!"@5$7$/%+%&%s%?$,F0:n$7$F$$$k$+%7%_%e%l!<%7%g%s�(B

�$B$K$h$j3NG'$7$F$*$+$J$$$H!"$J$+$J$+;W$$DL$j$K$OF0:n$7$^$;$s!#�(B

VGA�$B%b%8%e!<%kMQ$N%F%9%H%Y%s%A�(B vram_test �$B$r:n@.$7$^$9!#�(B

�$B%W%m%;%C%5%$%s%?%U%'!<%9$K$D$$$F$O!"�(BADDR�$B!"�(BDATAI�$B!"�(BRW�$B$K$D$$$F$O!"�(B

�$BE,Ev$JCM$rF~NO$7$F$*$-!"%a%b%j%"%/%;%9$,H/@8$7$J$$$h$&$K�(BMREQ=0�$B$H$7$F$*�(B

�$B$-$^$9!#�(B

VRAM�$B%a%b%j$N=i4|CM$,�(B "0" �$B$G$"$k$H�(BRGB�$B=PNO$+$i2?$b=P$^$;$s$+$i!"�(B

�$BE,Ev$J%-%c%i%/%?%3!<%I$G=i4|2=$7$F$*$-$^$9!#�(B

�$BA0%Z!<%8$G%3%T!<$7$F$*$$$?�(BVRAM20.mem�$B%U%!%$%k$K$O!"�(B

�$B$"$i$+$8$aJ8;z%3!<%I$,=q$-9~$s$G$"$k$N$G!"�(B

�$B$=$N$^$^%F%9%H$KMxMQ$G$-$^$9!#�(B

Verilog-XL�$B%7%_%e%l!<%?$rMQ$$$k>l9g$O!"�(B

initial

begin

$shm_open("waves.shm");

$shm_probe("as");

end

�$B$r=q$$$F$*$/$3$H$G!"2<0L3,AX$9$Y$F$N?.9fJQ2=$r%7%_%e%l!<%?$G4QB,$G$-$^$9!#�(B

--- vram_test.v ---

`timescale 1ns/1ns

module vram_test;

reg CLK, DCLK, RST;

reg [11:0] ADDR;

reg [ 7:0] DATAI;

reg MREQ,

RW;

wire [ 7:0] DATAO;

wire ACK;

wire [ 7:0] R, G, B;

wire HS, VS, DE;

initial

begin

$shm_open("waves.shm");

$shm_probe("as");

end

integer i;

initial

begin

CLK = 0;

for( i=0 ; i<3200000 ; i=i+1 )

CLK = #10 ~CLK;

$finish;

end

initial

begin

DCLK = 0;

while( 1 )

DCLK = #20 ~DCLK;

end

initial

begin

RST = 0;

RST = #5 1;

RST = #30 0;

end

initial

begin

ADDR = 12'h000;

DATAI= 16'h0000;

MREQ = 1'b0;

RW = 1'b0;

end

vram v1 (CLK, DCLK, RST, ADDR, DATAI, DATAO, MREQ, RW, ACK, R, G, B, HS, VS, DE);

endmodule

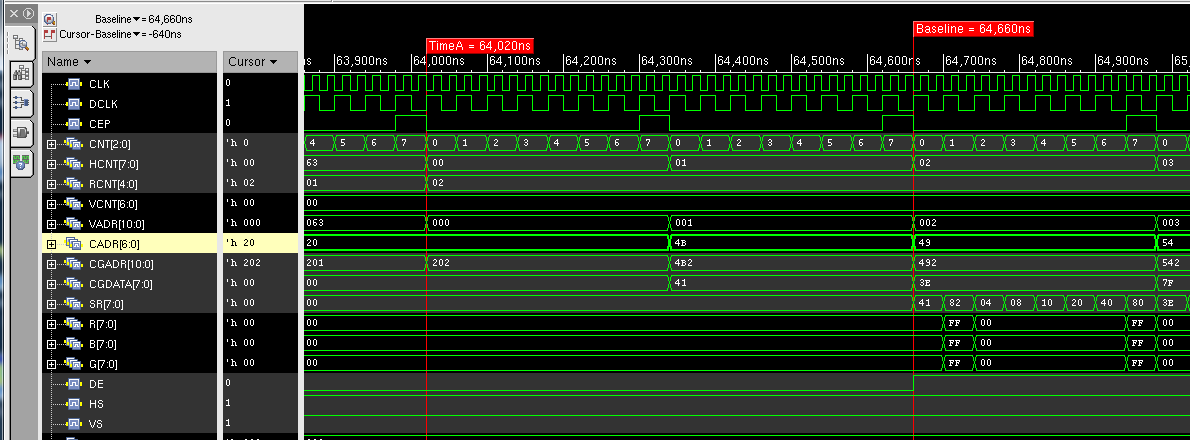

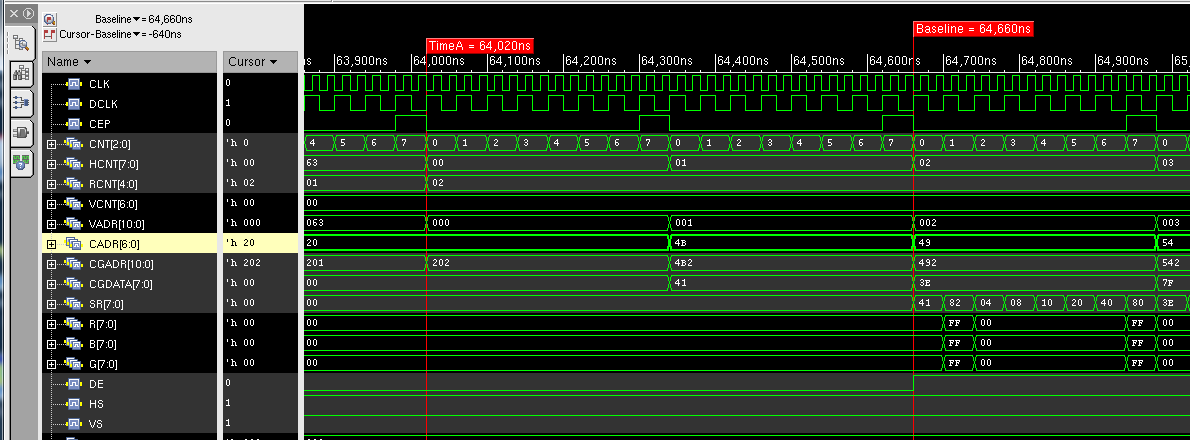

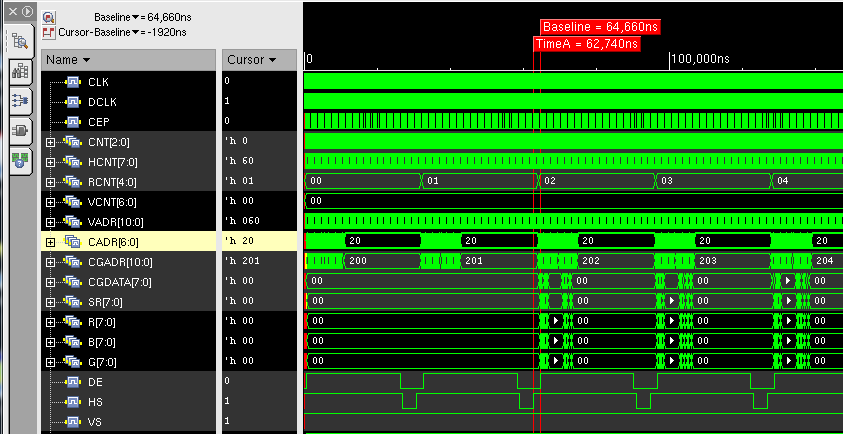

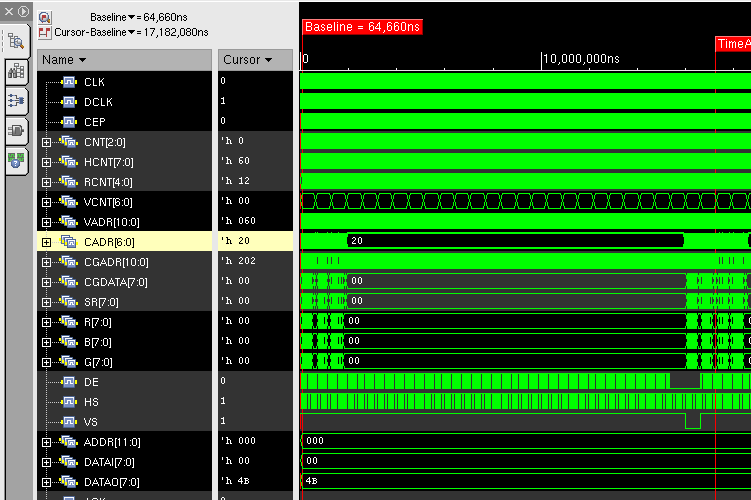

�$B%7%_%e%l!<%7%g%s$N7k2L$O0J2<$N$h$&$K4QB,$G$-$^$7$?!#�(B

TimeA�$B$N%+!<%=%k0LCV$,!$#19TL\$N�(B2�$B%i%9%?L\$,3+;O$5$l$?$H$3$m$G$"$j!$�(B

DCLK�$B$N�(B25MHz�$B$G�(B8�$B2s%+%&%s%H$7$?$H$-$K!"�(B1�$BJ8;zJ,$NI=<(=*N;%?%$%_%s%0�(B CEP �$B$,�(B

�$B=PNO$5$l$k$?$a!"$3$l$K$h$j%Q%$%W%i%$%s%l%8%9%?$H$J$k�(B CADR �$B$KI=<($9$k%-%c%i%/%?%3!<�(B

�$B%I$G$"$k�(B 0x4B �$B$,5-21$5$l$F$$$^$9!#�(B

�$B

�$B$3$NMM$K!"J8;z$N%G!<%?$O�(B2�$BJ8;zJ,%?%$%_%s%0$,CY$l$F=PNO$5$l$k$3$H$K$J$k�(B

�$B$?$a!$I=<(%?%$%_%s%0?.9f$G$"$k�(BDE�$B$,�(B2�$BJ8;zJ,CY$l$F=PNO$5$l$F$$$^$9!%�(B

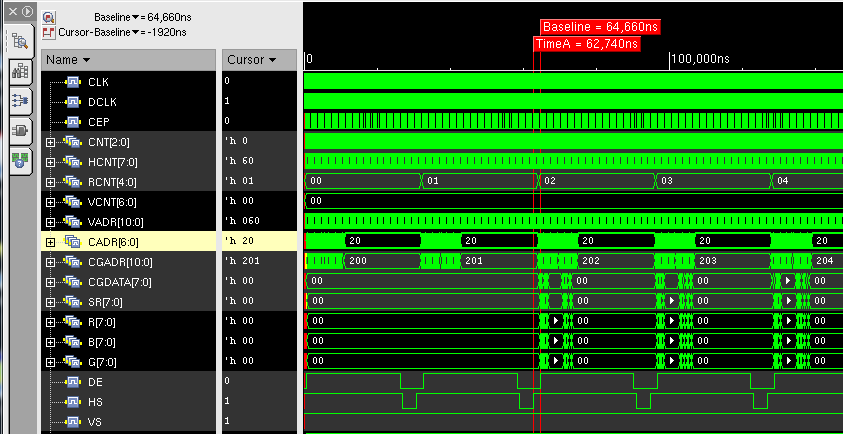

�$B;~4V$,?J$`$H!"?eJ?F14|%/%m%C%/�(B HS �$B$,IiO@M}$G=PNO$5$l$F$/$k$N$,J,$+$j$^$9!#�(B

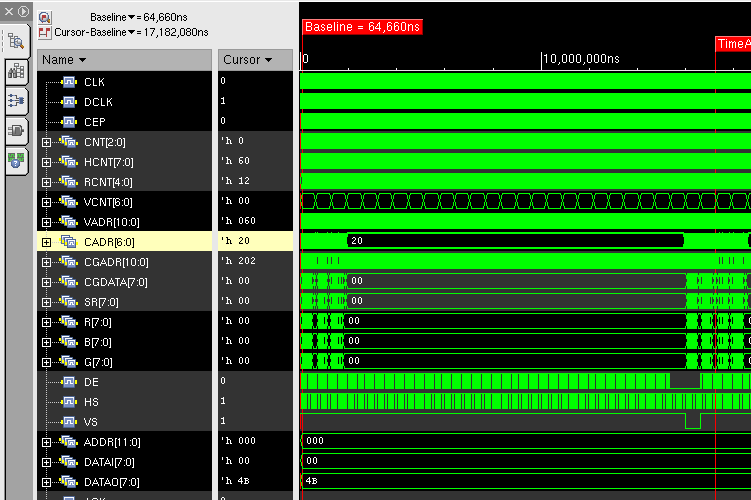

�$B$5$i$K;~4V$,?J$`$H!"?bD>F14|%/%m%C%/�(B VS �$B$,IiO@M}$G=PNO$5$l$F$/$k$N$,J,$+$j$^$9!#�(B

| Back |