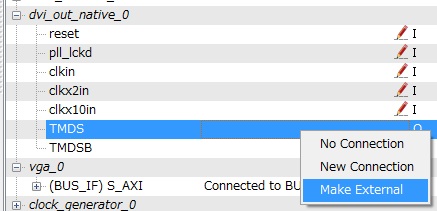

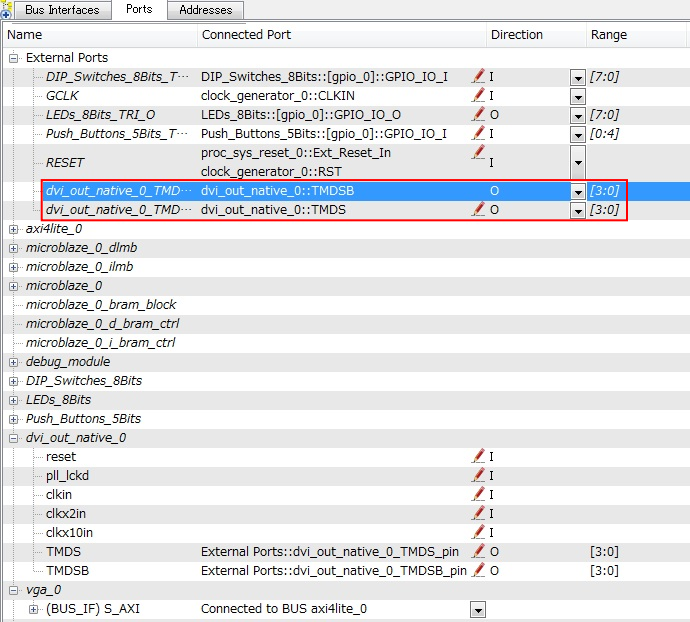

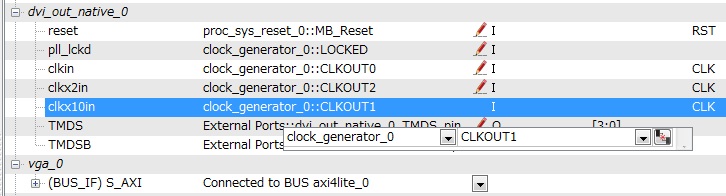

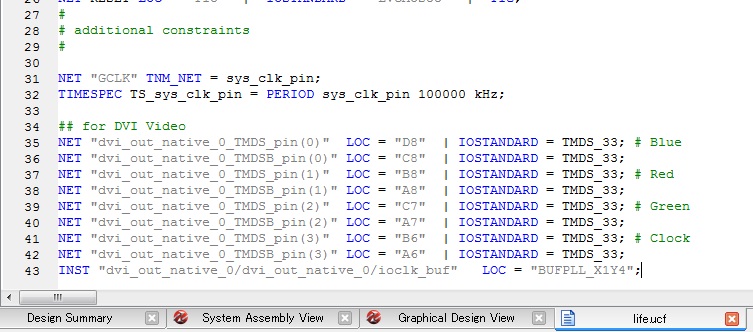

The configuration to allocate output terminals TMDS and TMDSB in the physical electric terminal of FPGA is described.

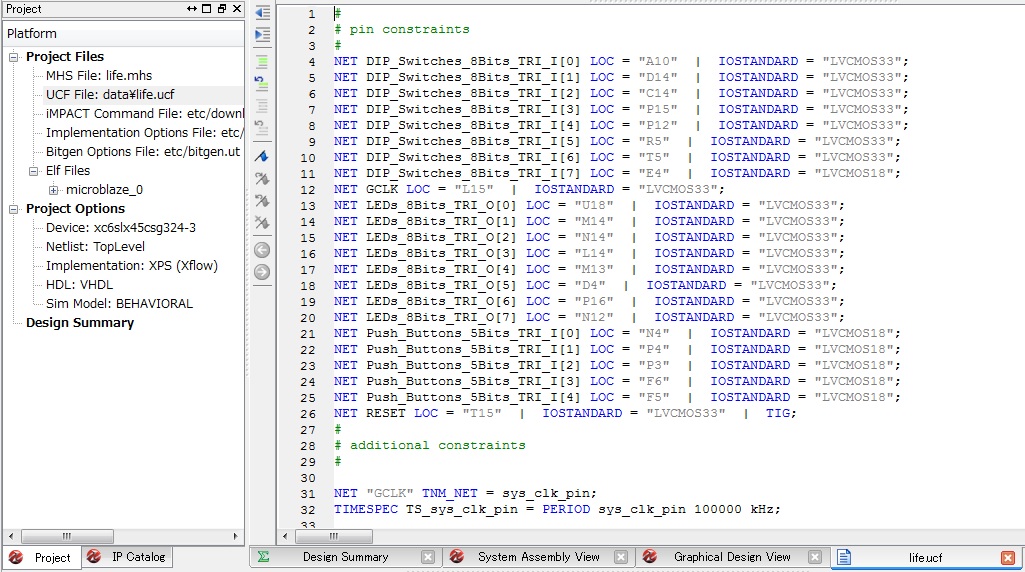

"UCF File of choosing "Project" tab : It clicks the office of productivity, technology and innovation of data/life.ucf" in the double.

The edit-display of the "life.ucf" file starts up.

It adds the following account to the office of productivity, technology and innovation of the last-line of the file.

## for DVI Video NET "dvi_out_native_0_TMDS_pin(0)" LOC = "D8" | IOSTANDARD = TMDS_33; # Blue NET "dvi_out_native_0_TMDSB_pin(0)" LOC = "C8" | IOSTANDARD = TMDS_33; NET "dvi_out_native_0_TMDS_pin(1)" LOC = "B8" | IOSTANDARD = TMDS_33; # Red NET "dvi_out_native_0_TMDSB_pin(1)" LOC = "A8" | IOSTANDARD = TMDS_33; NET "dvi_out_native_0_TMDS_pin(2)" LOC = "C7" | IOSTANDARD = TMDS_33; # Green NET "dvi_out_native_0_TMDSB_pin(2)" LOC = "A7" | IOSTANDARD = TMDS_33; NET "dvi_out_native_0_TMDS_pin(3)" LOC = "B6" | IOSTANDARD = TMDS_33; # Clock NET "dvi_out_native_0_TMDSB_pin(3)" LOC = "A6" | IOSTANDARD = TMDS_33; INST "dvi_out_native_0/dvi_out_native_0/ioclk_buf" LOC = "BUFPLL_X1Y4";After adding, it is as follows.

Press

Above, it is finished the hardware design of the system.

Next, it is layout process for embedded system.

| Back |Top |Next |